# Algorithmic Skeletons: Structured Management of Parallel Computation

# Murray I. Cole

Department of Computing Science,

University of Glasgow,

United Kingdom.

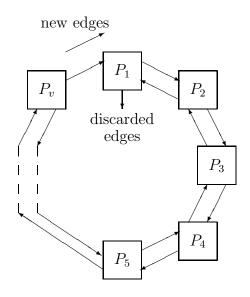

[Now of the Division of Informatics, University of Edinburgh. The text is reproduced on the WWW by kind permission of the publishers, MIT Press.]

# Table of Contents

| Abstract |                                                    | iv           |

|----------|----------------------------------------------------|--------------|

| Ackno    | wledgements                                        | $\mathbf{v}$ |

| Chapt    | er 1 Generating and Controlling Parallelism        | 1            |

| 1.1      | Introduction                                       | 1            |

| 1.2      | The Spectrum of Existing Systems                   | 3            |

| 1.3      | Conclusions                                        | 13           |

| Chapt    | er 2 Algorithmic Skeletons – A New Approach        | 15           |

| 2.1      | Motivation                                         | 15           |

| 2.2      | Algorithmic Skeletons                              | 19           |

| 2.3      | Parallel Hardware                                  | 22           |

| 2.4      | Implementation Structures and Performance Measures | 26           |

| 2.5      | Related Work                                       | 29           |

| Chapt    | er 3 The Fixed Degree Divide & Conquer Skeleton    | 30           |

| 3.1      | Introduction                                       | 30           |

| 3.2      | The ZAPP Approach                                  | 30           |

| 3.3      | Fixed Degree Divide & Conquer                      | 32           |

| 3.4      | Implementing the Skeleton                          | 33           |

| 3.5      | Analysis of Implementations                        | 39           |

| 3.6      | Partial Trees                                      | 44           |

| 3.7      | Examples                                           | 47           |

| Chapt    | er 4 The Iterative Combination Skeleton            | 52           |

| 4.1      | Abstract Specification                             | 52           |

| 4.2      | Parallel Implementation Issues                     | 55           |

| 4.3      | Implementation on an Idealised Grid                | 56           |

| 4.4      | Fixed Size Grids and Redistribution                | 64           |

| 4.5      | Redistribution with a Shortage of Objects          | 71           |

| 4.6          | Alternative Approaches                           | 76  |

|--------------|--------------------------------------------------|-----|

| 4.7          | Examples                                         | 77  |

| Chapte       | er 5 The Cluster Skeleton                        | 81  |

| 5.1          | An Alternative Approach to Skeleton Construction | 81  |

| 5.2          | Motivating a New Skeleton                        | 81  |

| 5.3          | Implementing the Skeleton                        | 85  |

| 5.4          | Exploiting the Cluster Skeleton                  | 91  |

| Chapte       | er 6 The Task Queue Skeleton                     | 93  |

| 6.1          | The Abstract Specification                       | 93  |

| 6.2          | The Structure of an Implementation               | 96  |

| 6.3          | Implementing the Queue                           | 100 |

| 6.4          | Implementing the Data Structure                  | 108 |

| 6.5          | Summary                                          | 113 |

| 6.6          | Examples                                         | 114 |

| Chapte       | er 7 Conclusions                                 | 120 |

| 7.1          | The Case for Skeletons                           | 121 |

| 7.2          | Future Directions                                | 123 |

| Bibliography |                                                  | 126 |

| Index        |                                                  | 130 |

## Abstract

In the past, most significant improvements in computer performance have been achieved as a result of advances in simple device technology. The introduction of large scale parallelism at the inter-processor level now represents a viable alternative. However, this method also introduces new difficulties, most notably the conceptual barrier encountered by the user of such a system in efficiently coordinating many concurrent activities towards a single goal. Thus, the design and implementation of software systems which can ease this burden is of increasing importance. Such a system must find a good balance between the simplicity of the interface presented and the efficiency with which it can be implemented. This book considers existing work in the area and proposes a new approach.

The new system presents the user with a selection of independent "algorithmic skeletons", each of which describes the structure of a particular style of algorithm, in the way in which "higher order functions" represent general computational frameworks in the context of functional programming languages. The user must describe a solution to a problem as an instance of the appropriate skeleton. The implementation task is simplified by the fact that each skeleton may be considered independently, in contrast to the monolithic programming interfaces of existing systems at a similar level of abstraction.

The four skeletons presented here are based on the notions of "fixed degree divide and conquer", "iterative combination" "clustering" and "task queues". Each skeleton is introduced in terms of the abstraction it presents to the user. Implementation on a square grid of autonomous processor-memory pairs is considered, and examples of problems which could be solved in terms of the skeleton are presented.

In conclusion, the strengths and weaknesses of the "skeletal" approach are assessed in the context of the existing alternatives.

# Acknowledgements

This book is a revised and extended version of my Ph.D. thesis. Many thanks are due to Gordon Brebner who supervised the original work at the University of Edinburgh. He provided timely encouragement and advice, carefully read and criticised numerous documents and was always prepared to listen to my ideas. Most importantly, Gordon has that invaluable asset of the good supervisor, an ever open door.

I was supported financially at Edinburgh by a Science and Engineering Research Council research studentship.

The material on skeletons as higher order functions has been developed since my arrival at the University of Glasgow. Particular thanks here are due to John Hughes for pointing out the connection between the two concepts.

Finally, I would like to thank Tom Lake for his careful and constructive observations during the revision process.

This book is dedicated to Ally, who knows why.

Murray Cole, Glasgow, 1989.

# Chapter 1

# Generating and Controlling Parallelism

### 1.1 Introduction

The task of designing and implementing any part of a computer system is essentially a process of abstraction. The facilities provided by an existing level are used to construct an implementation of an abstract level with its own, more desirable properties. In a complete system, many such levels are involved, ranging say from the design of transistors using the physical characteristics of semi-conductors to the provision of highly specialised user interfaces built upon some underlying level of software.

Each abstraction allows us to sacrifice a certain degree of freedom in return for a more useful and appropriate set of resources. In practice, this is reflected by a loss in performance of applications designed at higher levels over that which could be achieved (in theory) by direct implementation at a much lower level. Thus, a high level program subjected to a series of automatic compilations cannot be expected to run as quickly as some hypothetical alternative solution, written directly in micro-code for the same machine and exploiting every available short cut. On the other hand, the original problem may be so complex as to make the latter course impossibly difficult. In this way, the abstraction process can be seen to make a wider range of solutions accessible in practice (though not, of course, in theory). Furthermore, these higher level solutions reap significant gains in portability and clarity.

The inevitable decline in performance associated with abstraction has an important corollary to the effect that the bounds upon the level at which it becomes impractical to build further abstractions are dictated by the absolute performance achievable at the hardware level. As hardware power and reliability increases, it

becomes reasonable to move higher and higher levels of machine from the realms of theory into practice. For example, while it would have been possible to conceive of implementing a functional language interpreter on typical 1950's hardware, the resulting performance would have been uninspiring to say the least. Run essentially the same program on a machine many thousands of times faster and the abstraction suddenly provides a very useful, flexible tool.

The historical trends in hardware technology have been towards dramatically increased miniaturisation, speed and reliability. Complex components can now be mass produced at low cost. For the computer scientist, probably the most important development has been the erosion of the distinction between processor and memory technology, and the erstwhile mismatch in speed and cost between them. Computer architects may consider processing elements to be as readily available as were memory cells traditionally. Further technological developments will emphasise the new freedom. The revolutionary feature of VLSI (and what lies beyond) is not the increase in straightforward processing speed which it provides, although this certainly has an important place in the evolution of traditional systems. Far more significant is the fact that it is now quite possible to build computers in which thousands of processors operate concurrently to solve a single problem. It is now practical to increase raw performance by replication as well as by miniaturisation.

As an idea this is nothing new. In the very first issue of the Communications of the ACM, Saul Gorn [11] notes that:

"We know that the so-called parallel computers are somewhat faster than the serial ones, and that no matter how fast we make access and arithmetic serially, we can do correspondingly better in parallel. However access and arithmetic speeds seem to be approaching a definite limit ... Does this mean that digital speeds are reaching a limit, that digital computation of multi-variate partial differential systems must accept it, and that predicting tomorrow's weather must require more than one day? Not if we have truly-parallel machines, with say, a thousand instruction registers."

Thirty years on, the difference is that we can now construct such machines. However, Gorn also recognised the challenges that would be posed to the system designer by the new parallel computers:

"But visualise what it would be like to program for such a machine! If a thousand subroutines were in progress simultaneously, one must program the recognition that they have all finished, if one is to use their results together. The programmer must not only synchronize his subroutines, but schedule all his machine units, unless he is willing to have most of them sitting idle most of the time. Not only would programming techniques be vastly different from the serial ones in the serial languages we now use, but they would be humanly impossible without machine intervention."

Whereas previous developments have slotted into the existing system hierarchy with ease, providing increased performance within the recognized framework, parallel hardware asks new questions. To what extent should the new found concurrency at the lower levels be reflected in the abstractions built on top? If the answer is "substantially" then how is parallelism to be presented? If "not at all" then is it possible to harness the new processing power to simulate existing structures, but faster? How much faster? These are the questions underpinning the work presented in this book.

We are concerned with the process of designing and implementing high level programming systems which can exploit massively parallel hardware. Note that the word "systems" is used deliberately here in preference to "languages". We are more interested in the abstract computational model implied by a particular language than with a precise syntax. Depending upon the approach taken, the amount of real language design involved in the process can vary from none at all to the complete specification of a new language. We will see examples of both and of instances falling between these extremes in the material presented in the remainder of this chapter. The new approach proposed subsequently will be seen to fall towards towards the former end of the scale. It allows the bulk of a program to be described in an existing language, adding just enough super-structure to significantly ease the task of parallel implementation. In order to put these proposals in context, we begin with a review of existing approaches.

## 1.2 The Spectrum of Existing Systems

A variety of techniques are currently being used to address the problem of building higher level programming systems upon parallel hardware. When less important details are filtered out, the resulting systems fall into three rough categories.

The level of abstraction in the first category is high. Users of these machines are not required to deal with parallelism at all and need have no knowledge of the implementation to make use of the system. In the second category the degree of abstraction is reduced. Here, users are required to present explicitly parallel solutions. However, in doing so they are allowed certain freedoms not afforded directly by the hardware. The third category contains systems in which the user is required to specify solutions which use parallelism in a style very close to that physically present.

The use of a parallel computer to tackle some problem involves encounters with several well known sources of difficulty. The designer of a parallel programming system must decide which of these to handle implicitly and which to leave to the programmer. In the ensuing discussion we will consider the choices made in the design of existing systems. It will become clear that these essential problems are inextricably interwoven and that it makes little sense to consider any one in isolation. However, in order to set the scene and clarify terminology, we will briefly present the main characteristics of each.

The most fundamental and obvious task is that of problem decomposition, the identification of parallelism. Processes must be described which can operate concurrently to achieve a solution, or some indication of how these can be generated dynamically must be found. We should be certain (or at least very confident, in less predictable circumstances) that the parallel solution will be faster than a traditional sequential solution! Unfortunately, the eventual performance will be governed by a host of other implementation issues but an optimistic starting point is clearly essential.

The second problem is that of *distribution*, the physical exploitation of the potential parallelism identified by decomposition. We must specify a mapping from operations which may be executed concurrently to the available processors, or as before, indicate the mechanism by which this mapping can be achieved dynamically.

It is most unlikely that decomposition and distribution of a problem will lead to a situation in which a large number of processes perform entirely independent operations upon entirely independent data. More realistically, our parallel processes will perform sequences of similar or identical tasks upon data which is shared, to a greater or lesser extent. The third problem to be addressed is that of implementing this *code and data sharing*. The obvious choice is between the replication of information (with the associated costs in space and consistency maintenance) and direct sharing (with the problems of granting and controlling access efficiently).

Finally, it is necessary to consider the precise mechanisms by which the sharing of resources (whether code or data) is to be described and controlled. *Communication* and *synchronization* underlie the whole notion of concurrent operation and will be present in at least one and probably many levels of any parallel system.

We are now in a position to examine the relevant characteristics of our three categories more closely. In doing so, we inevitably omit many other fascinating aspects of the systems involved. References [29, 4, 2, 10] provide good starting points for further reading.

#### 1.2.1 Highly Abstract Systems

The first category contains systems in which the abstract machine presented to the user is entirely devoid of parallelism and is completely isolated from the underlying implementation mechanism. Such systems typically present functional, logical or data-flow models of computation. They are often referred to as being "declarative" systems, since the programmer makes a series of declarations which define the properties of a solution to some problem, rather than specifying a precise series of operations which will lead to the solution. Thus, languages of this type (at least in their pure forms) are not only non-parallel but also non-sequential, having no notion at all of a flow of control.

All truly functional languages are based on the lambda calculus. This is a very simple, but powerful language of expressions and transformation rules on expressions. The only objects present are identifiers, single argument function definitions ("abstractions") and applications of functions to arguments. A "program" consists of a collection of such objects and its execution amounts to evaluating the result of applying a top-level function to an argument. This type of function application is the only operation present and involves the replacement of a function-argument pair with a copy of the function body (from its definition) in which occurrences of the "dummy" or "free" variable have been replaced by copies of the actual argument (which may of course itself be a function application). Functions and arguments may be nested. This simple system can be shown to provide as much computational power as any other fundamental computing mechanism (e.g. the Turing machine). A particularly powerful aspect of the model is the ability to define "higher order functions", to which we will return in chapter 2. Other convenient features such as multiple argument functions, localised definitions and data structures may all be defined as lambda expressions.

In the same way, a high level functional program is simply a function definition which refers to other functions in its body. A "call" of the program involves supplying arguments to this function and "execution" consists of employing the function definitions (conceptually using the application by substitution technique from the lambda calculus) to obtain an alternative, but equivalent representation of the function and arguments pair. This "output" is simply a more useful representation of the original program and "input", in the way that "6" is a more useful representation of "(4-2)\*3".

The important point is that execution may progress from the initial to the final representation in any fashion which maintains equivalence. In particular, it will often be possible to execute many parts of the transformation concurrently since the conventional problems associated with changes of state have been discarded along with the notions of state and store themselves (at least at this abstract level). An obvious way to represent the program as it evolves is as a graph, in which nodes represent function applications. The children of a node are the arguments of the corresponding application. The process of expanding and contracting the graph (i.e. program evaluation) is referred to as "graph reduction".

With this approach, the task of decomposition to generate parallelism is simple. The abstract execution model allows candidate nodes to be expanded at any time, while function applications may be evaluated as soon as arguments are available. Thus, a potentially parallel process is generated every time a node reaches one of these states.

It is important to realise that this does not imply that every functional program is actually highly parallel. As a trivial example, consider defining a function to compute factorials. The obvious definition will look something like this:

```

factorial\ 0 = 1

factorial\ n = n * factorial\ (n-1)

```

Such a function would execute sequentially on a typical graph reduction machine, irrespective of the number of available processors. A more complex definition notes that

```

\begin{array}{lll} factorial \ 0 &= 1 \\ factorial \ n &= product \ 1 \ n \\ product \ a \ a &= a \\ product \ a \ b &= (product \ a \ \lfloor \frac{a+b}{2} \rfloor) * (product (\lfloor \frac{a+b}{2} \rfloor + 1) \ b) \end{array}

```

which produces significant potential parallelism. Although declarative systems involve no explicit notion of execution sequence, it is unfortunately clear that some knowledge of the execution mechanism can be used to great effect by the programmer.

The main problem for the implementor of a functional system comes with the realistic distribution of the available parallelism. In graph reduction, the structure of the graphs produced is specific to each problem instance. Furthermore, this structure only becomes apparent during execution and evolves dynamically. Thus any mapping scheme which tries to distribute the graph and the associated workload effectively must be both dynamic and general purpose. This problem can be tackled in two ways. The first approach [16] attempts to balance work dynamically in a localised manner by allowing idle processors to grab work (effectively portions of the expanding graph) from busy neighbours. Contrastingly, schemes such as [7] take a more global view. The graph is stored as a globally accessible "pool

of packets" which in practice is distributed across the local processor memories. An interconnection network deals with accesses to non-local packets. There is a difficult trade-off here between the locality of access and lack of global scheduling of the former method, and the more complicated global access and distribution of the latter.

An alternative approach [15] recognizes the difficulty of automating distribution and allows the introduction of program annotations which provide a means of influencing the execution mechanism. These are guaranteed to preserve the semantics of the computation, but may improve its efficiency. Such additions may be argued to move the model out of this category, in that the programmer is now partly (or even wholly) responsible for the task of decomposition. Similarly, [20] discusses a language which allows program partitioning and interconnection structure to be described in a declarative style.

The distinction between "data" and "code" in a functional system is blurred – both are intermingled in the graph during expansion, reflecting their common foundations in the lambda calculus. However, it is possible to recognize that the function definitions play a more static role, in some ways similar to that of more conventional code. They provide templates describing the expansions and reductions which may be applied to the graph. Most systems [7, 16] provide each processing element with a copy of all the function definitions which may be used during execution to manipulate independent areas of the graph concurrently.

A functional program contains no explicit notions of communication or synchronization. However, in a realistic implementation these are introduced as a by-product of decomposition, distribution and sharing, and must be handled by the system itself (and consequently by the implementor of that system).

The data flow model of computation [9] arrives at a similar point to graph reduction by a different route. Here the underlying principle is the representation of a computation as graph of "operator" or "instruction" nodes connected by edges along which data items flow. Each node receives data "tokens" along its input edges, performs some simple calculation and distributes resultant data tokens on its output edges. The basic control mechanism is that a node may only perform its operation once it has received data tokens on all of its inputs. Thus, nodes may execute in parallel, subject only to the availability of data. A typical data-flow graph will be re-entrant and for any realistic problem, there will probably be more operator nodes in the graph than there are available processors. The processes of associating output tokens with appropriate operator nodes and of deciding which are ready for execution is known as "matching". Ready operators

must then be selected for actual execution. These processes are usually separated (at least in principle) from the "execution units".

The important difference between this approach and those discussed above is that whereas a graph reducer manipulates the graph by modifying both data and the "instruction code" itself, a data flow graph is statically defined by the program and only data is manipulated. Languages built upon these concepts are still "functional" but may be dressed up to resemble (at least superficially) sequential imperative languages [3], particularly if "scientific" applications are envisaged. The compilation process from high level language to the underlying data-flow graph has some similarity to the process of expansion in graph reduction and amounts to the decomposition phase of parallel implementation.

There is nothing analogous to the function definitions of functional language schemes, since these have been compiled away. Consequently all the problems of distribution, communication and synchronization are associated with the data-flow graph and the interactions between its node operators. Although the structure of the graph is static, it will only be apparent during (or even after) execution that some sections of the graph were more active than others. Thus, a good distribution scheme is difficult to obtain. Existing solutions follow the two patterns observed in the functional case in choosing whether or not to attempt to localise operations upon certain portions of the graph to particular processors.

Finally, logic languages are based on Horn clauses, a restriction of first order (predicate) logic. The model of computation centres on the definition and investigation of relationships described as predicates, among data objects described as arguments to these predicates. In similar fashion to functional programming, the specification of a computation consists of a collection of such predicates and their associated clauses. The role of the outermost function application, whose value is assessed in a functional system, is now played by the outermost predicate together with its arguments. Given fixed arguments, the interpretation is similar – "execution" consists of deciding whether the predicate is true given the arguments and the associated definitions. More interestingly, it is possible to specify the outermost predicate with unbound arguments. The purpose of execution is now to find bindings to the arguments which allow the predicate to be satisfied, or to determine that no such bindings exist.

At an abstract level, the process of evaluation may be seen as expanding and searching a tree of possibilities presented by consideration of the various dependencies between appropriate predicates and clauses. As with graph reduction, the semantics of pure logic languages often allow this process to proceed at many

#### 1.2.2 Idealised Parallel Systems

The systems discussed in the first category were characterised by the isolation of the abstract (or idealised) design space seen by the programmer from the parallel, distributed implementation. The second category considers machines in which the two levels are closer together and in particular, those in which the programmer's world includes explicit parallelism. The programmer is now responsible for decomposing the solution into a collection of concurrent processes. The abstraction remaining is concerned solely with the mechanisms by which such processes cooperate, and may take one of two closely related forms.

In the first, all processes are presented with equal access to some kind of shared memory space. In its loosest form, any process may attempt to access any item at any time. A variety of refinements of the scheme exist, each with its own rules defining the semantics which resolve or forbid clashing access requests. In a typical model, each such access is assumed to take unit time. The implementation task is to devise a scheme which can satisfy any legal combination of requests within some reasonable time on the realistic machine.

The second flavour of idealised machine discards shared memory based cooperation in favour of some form of explicit message passing. Typically each process is given the power to pass a message to any other in unit time, concurrently with a collection of other such exchanges (i.e. a complete communication network is assumed to exist). Once again the implementation task is to mimic such behaviour in reasonable time.

In the "shared memory" camp, much theoretical work on parallel algorithms focuses on the use of a variety of classes of idealised parallel machines (e.g. see [10]). Such machines consist of a collection of n standard uni-processors each with its own local memory. Additionally, they have access to an m location shared memory (SM), upon which they may operate during any instruction, with a variety of rules governing conflicts. In the most restrictive case, exclusive-read exclusive-write (EREW), no two processors may attempt to access the same shared memory location during the same time step. Concurrent-read exclusive-write (CREW) machines allow an arbitrary number of read accesses to the same location but require writing to be unique, while CRCW models allow completely arbitrary access to any locations during the same time step. Again, a variety of schemes govern the semantics of clashes, ranging from those in which a write clash results in a random (i.e. junk) value being recorded, through those in which

processor is chosen deterministically (e.g. by highest processor identity or smallest written value). The result of a read coinciding with several writes can be similarly defined. Some models augment the instruction set to include operations such as "fetch and add". Concurrent execution of several such operations on some location l produces the same result as if the instructions had been executed in some unpredictable sequential order. Thus, each participating processor receiving a copy of the original contents of l incremented by a unique subset of the other "added" values, while l itself has its contents incremented by the sum of all the values specified in the instructions.

a randomly selected processor is successful and on to those in which the successful

Proposed implementations of such machines associate each processor with a real sequential processor and its own local memory. The real processors are typically connected by some sparse network with unit time fixed length message passing between immediate neighbours only. Any other communications are forwarded through the network to their destinations. Since in reality there is no centralised memory, the idealised SM locations must be distributed across the local memories. Processors are required to cooperate in the simulation of the access patterns specified by each idealised step.

Straightforward solutions map each SM location to a single local memory location. Thus, simulation of a particular memory access requires message passing between the active processor and the one responsible for the location. Realisation of a complete idealised step is therefore reducible to the problem of concurrently routing a set of such messages around the network. This is closely related to the issue of sorting on networks and a variety of routing schemes have emerged, each with particular networks in mind. Useful results are obtained by the introduction of hashing techniques [26] to generate the shared to local memory mapping and of randomising routing phases [37] intended to alleviate the problems associated with awkward message permutations. In spite of good average or expected behaviour, any such scheme is vulnerable to steps in which all processors attempt to access locations stored by the same real processor. These can occur whenever  $m \geq n^2$ , and for fixed degree networks immediately imply an n fold simulation slow down, a performance level which could be matched by a single processor<sup>1</sup>.

A proposed remedy to this problem [26] is to keep multiple copies of each SM location in different real processor memories and to access only the most convenient. Initially this was proved successful only for dealing with multiple

<sup>&</sup>lt;sup>1</sup>This is true even of EREW models, since it is not necessary that the n requests refer to the same location but merely to the same processor's local memory.

reads. However, in a striking paper Upfal and Wigderson [36] show that the technique can be efficiently extended to include concurrent write steps. Several practical projects, such as the New York University "Ultracomputer" [12] have drawn from this pool of theoretical ideas.

The occam language [18] <sup>2</sup> takes a contrasting standpoint which bases cooperation on explicit process to process message passing, with no shared memory. Although theoretically close to the shared memory model, the point-to-point communication scheme encourages a different approach to problem solving. An occam process may be connected to any number of others by one way communication channels. A process runs asynchronously, accessing only its own exclusively local memory until it wishes to communicate with another process. Communication of some message down a channel takes place only when both sending and receiving processes indicate readiness (by attempting to execute output and input statements respectively). The sending process specifies the message, while the receiving process indicates the location in its memory where the new value should be stored. In this manner, explicit synchronisation of processes can be achieved. Write clashes are explicitly prohibited by a syntactically enforced rule which forbids processes running concurrently to write to common shared variables.

The occam programmer is required to consider the decomposition of data into independent sets in addition to the decomposition of work into processes. Any sharing of data must be programmed explicitly by message passing. In theory, occam programs allow any complexity of process connection network, including complete interconnection.

In terms of handling the key issues in the use of parallelism introduced previously, the machines in this category exhibit a clear shift in responsibility from system to user. No support is provided for problem decomposition, with the programmer explicitly specifying the processes which may operate concurrently. There is a split over the issue of data sharing. In the shared memory abstractions all data is shareable and the system takes responsibility for implementation. In those without shared memory, the user is required to partition data between processes and handle sharing explicitly by message passing. Code sharing is not an issue, while only the non-shared memory machines typically provide facilities for explicit inter-process communication. The burden here is still carried by the system which provides abstractions to more general networks than are physically present in hardware.

Finally, a variety of approaches are evident to the issue of synchronisation.

<sup>&</sup>lt;sup>2</sup>occam is a trademark of the INMOS group of companies.

At one extreme, the straightforward progression through a shared sequential program provided in several theoretical models relieves the user of any difficulty. The system handles the problem of bringing together divergent threads introduced by data dependent branching. The occam model requires any synchronisation to be expressed explicitly but the semantics of its communication primitives make this relatively simple. The more practical shared memory models are the least helpful here, requiring careful use of shared variables to ensure process rendezvous, though instruction sets augmented by "fetch and add" style instructions are useful.

#### 1.2.3 Low Level & Restrictive Systems

The final category completes the journey through the levels of abstraction afforded by parallel systems. It includes systems in which the user is required to consider both explicit parallelism and the realities of the hardware topology in designing a solution.

The Meiko Computing Surface [25] is a good example. Computing power is provided by a large collection of independently programmable processing elements, each with private local memory and four bi-directional communication channels. All channels are linked to a central switch where they may be connected in pairs to realise any network of degree four between the processors, as specified by the user. An occam solution to the problem in hand is constructed, but the user is responsible for the explicit mapping of occam processes to processors and channels to actual communication links. Thus, while communication between processes sharing the same processor is unlimited, actual parallelism between them is non-existent. On the other hand, communication between genuinely concurrent processes (on distinct processors) is restricted by the selected topology.

Turning to the key issues, it is clear that systems such as this represent a completion of the transition from system to user responsibility. The programmer is entirely responsible for problem decomposition and distribution. Code sharing will be implemented by simple replication, while any data sharing and communication required must be programmed explicitly with direct reference to the physical machine topology. Some support for the mechanics of synchronisation may be provided (e.g. by machines which run occam code on each node) but it will be up to the programmer to determine how and when to use this.

### 1.3 Conclusions

The preceding section categorised approaches to the problem of providing a useful, general purpose programming model combined with an implementation efficiently harnessing the computational power of parallel hardware.

The highly abstract approach of the first category has the obvious advantage that the user specifies solutions in familiar, well understood languages, free of concurrency. Against this must be weighed the difficulties of implementation and the corresponding loss of power over that available from the bare hardware. The fact that the degree of exploitable parallelism is dependent upon the program and is variable throughout execution makes problem independent analysis extremely difficult. Existing experimental results (e.g. [22]) report on only relatively small scale machines.

Algorithms used to implement the idealistic parallel machines of the second category are far more amenable to traditional analyses of time complexity. The algorithms usually involving routing and sorting across networks and it is often possible to estimate worst case performance to within a constant factor. Often an algorithm's complexity will be independent of the details of the particular step being simulated. In these cases it is possible to provide accurate estimates of the run time for a complete user program by multiplying the number of idealised steps by the simulation slow-down per step. Thus, in return for the effort of specifying an explicitly parallel solution, the user is rewarded with a more concrete estimate of run time. On the other hand, the standard overhead is incurred whether or not a particular program uses the full power of the simulation.

Contrastingly, the explicitly parallel systems in the third category incur only constant overheads, since there is no significant implementation cost. Programs are mapped directly onto the hardware by the user, performing as expected, and a cunning solution can extract the maximum achievable performance. In practice there are many examples of processor networks whose topology is especially well suited to the structure of certain problems.

In summary, existing systems either present a relatively friendly abstraction with hidden, unpredictable overheads (the first category), a harder to use abstraction still with in-built but better understood overheads (the second category) or a low-level, awkward abstraction essentially without overheads.

While varying widely in the degree of machine independence provided, all of these approaches share one common principle. In each case, the programming model presented to the user is intended to be "universal" in the sense that its full range of mechanisms may be used in the specification of any computation. In the more abstract machines this freedom has the result of allowing the description of computations which will be difficulty to implement in parallel. In the low level machines, geared directly towards parallel implementation it produces systems which are hard to use in many situations. The work presented in the subsequently proposes and investigates a new approach to the problem, based on the rejection of the concept of a single, universal programming model.

# Chapter 2

# Algorithmic Skeletons – A New Approach

In this chapter we introduce the "algorithmic skeleton" as the concept which will underpin our proposed approach to the provision of high level programming systems for parallel machines. We begin by discussing the lessons which can be learned from the survey introduced in chapter 1 and consider their implications. Section 2.2 describes the overall structure of the new approach.

In subsequent chapters we will present specifications and possible implementations of four candidate skeletons. Consequently, section 2.3 introduces the model of parallel hardware upon which the implementations will be built, while section 2.4 discusses the methods which will be employed in their construction and the measures which will be used to predict their efficiency.

## 2.1 Motivation

In the first chapter we considered a variety of programming systems which shared the goal of facilitating the efficient use of parallel hardware. Our investigation focussed on the issues of problem decomposition, distribution, code and data sharing, communication and synchronisation. We examined the ways in which particular systems divide responsibility for these between implementation and programmer. In retrospect, the resulting categorisation may be seen to be closely linked to the way in which systems handle the first two issues. Thus, in the first category full responsibility for both is allocated to the implementation, the second category leaves decomposition to the user but handles distribution in the implementation, while the third category makes the programmer deal with both. This neat correspondence should not be surprising, since decomposition and distribution are clearly the two most fundamental issues involved. While

solutions to the other problems are important and will have serious implications for performance, the type of sharing and communication required is determined by the way in which decomposition and distribution are handled. Without a parallel algorithm there can be no messages to exchange or data to share.

More importantly, the survey also illuminated one common principle which unites all categories. This is the notion that the model of computation and its associated programming constructs should be "universal" in the sense that they may be employed unrestrictedly in solving any problem. The motivating thesis for our new approach is that this "universality" is at the root of the serious difficulties encountered by existing approaches when dealing with problem decomposition and distribution. Thus, at the more abstract end of the spectrum, the expressiveness of the languages allows the programmer to specify computations which are either inherently sequential or so obscurely parallel that any realistic implementation will struggle to find a good decomposition and distribution strategy. As the simple "factorial" example demonstrates, this can be true even if the problem itself does admit an implicitly parallel solution. At the other end of the spectrum, systems targeted towards specific hardware have such restrictive models of computation (e.g. "anything that looks like a hypercube") that the programmer may struggle to find good solutions to problems with anything but the most natural and obvious decomposition. Between these extremes, the difficulties are more equitably shared between system and programmer, but must still be overcome.

Following from this analysis of the situation, we are tempted to conclude that the provision of a single, universal programming framework is incompatible with the goal of uniformly efficient parallel implementation. If the latter property is to remain a target then we must discard the former. However, our rejection of "universality" should not also throw out the high level of abstraction and machine independence which we associate with good systems. Indeed, our target system should not even be explicitly parallel, since we have already noted that problem decomposition is a difficult task for the programmer. Our goal then, is to define a programming system which, while appearing non-parallel to the programmer, admits only programs which it can guarantee to implement efficiently in parallel.

The solution which we propose draws its inspiration from two sources. Firstly, we note that the challenge of designing good algorithms in a purely sequential context has been the subject of extensive study. As experience has grown, a selection of generalised algorithmic techniques has emerged, each well suited to a certain variety of problems but inappropriate for others. For example, we are

familiar with concepts such as "divide and conquer", "dynamic programming" and more recently "simulated annealing". When investigating a new problem we may try to formulate a solution in one of these well known styles. Since we already know how to implement the essential computational structure of each technique, it will only be necessary to introduce problem specific details to produce a new, tailor-made program.

An analogous process can provide the foundation of our new system. We must identify a similar collection of algorithmic techniques, each having a computational structure which lends itself specifically to parallel implementation. Thus, if the essential structure can be parallelized, then any instantiations of the technique dealing with real problems will also share this property. This is already beginning to happen. In particular, the inherently parallel qualities of "divide and conquer" have been noted [22, 28, 14]. However, to produce the kind of idealised system envisaged above, we must go one step further than the development of a new set of parallel programming "folklore", describing such good techniques. Instead, we must aim to embed them within the syntactic structure of the programming model in a way which forces the programmer to use one or other of them as the central structure of every program. Furthermore, we would ideally like the programmer's visualisation of these structures to be non-parallel.

Our second source of inspiration suggests a means by which we can achieve this strict enforcement in a coherent, high-level way. This is the concept of "higher order" functions which is central to the expressive power of pure functional languages. We now present a brief introduction to "higher order functions", for the unfamiliar reader.

Simple functions accept items of some data type as arguments and return items of some data type as results. For example, the integer square function defined

$$square x = x * x$$

takes an integer as its argument and returns an integer as its result. The type of this function can be denoted

$$square: int \rightarrow int$$

Some simple functions are able to operate upon items of more than one data type because the operations they perform do not inspect the details of the argument but only its "structure". A good example is the function "head" which takes a list of items of some particular type as its argument and returns the first item on the list as its result. Clearly the type of the items themselves is of no consequence

and such functions are said to be "polymorphic" <sup>1</sup>. Their type can be denoted using dummy symbols to represent arbitrary types. Thus, "head" has type

$$head: [a] \rightarrow a$$

where square brackets denote "list of" and "a" stands for any type.

Higher order functions are slightly more complicated. Rather than taking and returning simple data items, they accept other functions as arguments and return new functions as results. The function which is returned is a structural composition of the argument functions and possibly some others. Probably the simplest and most commonly used higher order function is "map". The single argument required by map is some function f with type

$$f: a \rightarrow b$$

Remember that a and b can be any, possibly identical, types. The result of applying map to such an f is another function "map f" of type

$$(map\ f):[a]\to[b]$$

that is, a function which has a list of elements of type "a" as its argument and returns a list of elements of type "b". The effect of " $map\ f$ " is to apply "f" to every element in the argument list, placing the result in the corresponding position in the result list. For example, " $map\ square$ " would have type

$$(map\ square): [int] \rightarrow [int]$$

and would return the list of squares of the integers in the argument list. The important point is that we can regard "map" as a function in its own right, with type

$$map:(a \to b) \to ([a] \to [b])$$

i.e. a function which deals with other functions rather than simple data types.

Higher order functions are precisely the kind of object which we seek to give a more solid basis to our notion of "generalised algorithmic techniques". They do not concern themselves with the lowest level details of particular problems. Instead, they capture the higher level computational structure of whole classes of algorithm. Solutions to particular problems can be instantiated by supplying the "customising" argument functions appropriate to the task in hand. Thus, we can equally well use map in conjunction with some other simple function to

<sup>&</sup>lt;sup>1</sup>i.e. "having many forms"

produce a different result, using a method which has the same overall structure. For example, given a function "uppercase" which returns the uppercase equivalent of its lower case character argument

$$uppercase: char \rightarrow char$$

we can easily use "map uppercase" to transform a list of characters in the same way

$$(map\ uppercase): [char] \rightarrow [char]$$

The high-level algorithm is identical to that of "map square" with only the lower level details differing. In other words, the use of "map" ties down the essential structure of our computation, while its argument function produces a problem specific program which solves the task in hand.

## 2.2 Algorithmic Skeletons

While higher order functions fit snugly into the syntactic framework of functional languages, we can also imagine a similar facility in the context of conventional imperative languages. Here, a higher order function could be represented as a program or procedure "template", specifying the overall structure of a computation, with gaps left for the definitions of problem specific procedures and declarations. The fit would be somewhat better in languages which allow procedures to be passed as parameters. Thus, the system which we are about to propose could be presented to the programmer in the context of any "base" language, whether declarative or imperative. Our subsequent use of the term "higher order function" should be interpreted with this freedom in mind.

The programming model which we intend to investigate can now be described. In this model, the programmer is presented with a selection of specialised higher order functions (or similar, depending upon the base language) from which one must be selected as the outermost function in the program. The programmer may then use the full power of the language to describe the functions to which the selected higher order function will be applied to produce the problem specific final program. The restriction on program structure imposed at the highest level is the means by which we curb the "universality" problem. Only those programs whose outermost structure matches one of the acceptable higher order functions are legal. Having achieved this restriction, we will not be concerned with the lower level details of program, since these will not affect the essential structure of the algorithm or its implementation. Thus, the full power of the "host" language can be made available at these levels. We will refer to each suitable higher

order function as an "algorithmic skeleton", since it describes the computational skeleton of an algorithm without overspecifying the details.

It would be quite easy to provide such a facility in a conventional environment, with no thought to parallelism. We would define "skeletons" for all the familiar algorithmic paradigms and support each with an optimised machine code implementation into which the problem specific user code would be plugged automatically. The key to achieving efficient parallel performance for such a model is to ensure that each of the permissible higher order functions describes a computational structure for which we can find an efficient parallel implementation, irrespective of the problem specific details. In other words, it should correspond to a good parallel "algorithmic technique". Of course, the actual specification of each skeleton as seen by the programmer need not (and ideally should not) be explicitly parallel. It is sufficient that it be equivalent to some other explicitly parallel "skeleton" which the system knows how to implement.

If we are to avoid falling into the trap of trying to implement a universal language automatically, it seems that we must restrict ourselves to exploiting only the parallelism inherent in the basic structure of each skeleton. The lower level problem specific functions may or may not be parallelizable, but we should ignore them, since to attempt deeper analysis leads us into the the original trap of "universality". The implementation task is to parallelize the distribution and manipulation of data implied by the highest level structure, leaving other functions to be executed entirely sequentially on individual processors as required, just as user code would slot directly into the structure of an entirely sequential implementation. This approach has two subsidiary benefits. Firstly, the choice of language used to describe the problem specific details is only restricted by the availability of compilers for the sequential processors which comprise the parallel machine. Secondly, we can always take advantage of the best such compiler, since the generated code is not required to interact with the parallel super-structure.

In summary, the programmer sees each skeleton as a higher order function (or program "template" if the base language is imperative) which is one of a collection of algorithmic tools from which a problem specific program must be fashioned. Meanwhile, to the system implementor, each skeleton is a generic computational pattern for which an equivalent, efficient parallel "harnesses" must be defined. Just as conventional languages require different compilers for different machines, so each skeleton will require a different implementation for each parallel machine. As with conventional compilers, these differences will be invisible to the programmer, who always sees the same machine independent programming

framework.

In order to contrast our approach to those discussed earlier, it is instructive to consider the ways in which the issues of problem decomposition and distribution are handled. The key observation is that the parallel decomposition is already implicit in the structure of each skeleton. Thus, in selecting a particular skeleton (which may either be explicitly declarative or imperative and sequential), the programmer is also unwittingly selecting a parallel problem decomposition. Similarly, the task of distribution has been reduced to the problem of implementing each of a selection of pre-defined decomposition patterns, one per skeleton. Since these must only be implemented once (for each hardware topology), they can be carefully hand-crafted to extract maximum performance. All complete programs written in terms of the same skeleton will use the same pre-defined implementation structure with its in-built distribution strategy. Thus, in selecting a skeleton, the programmer is also selecting an associated distribution plan.

We may throw further light on the proposal by imagining an interactive session with a "programming environment" which could be constructed around such a model. Upon activating the system, the programmer might be presented with a menu listing the available skeletons. Just as with a conventional programming language, details and examples of these would be described in the accompanying user's guide. An appropriate skeleton for the problem in hand would be selected. Similarly, the programmer would select a base language in which to specify the procedures and data structures fleshing out the skeleton. The system would respond by displaying the generic program which describes the operation of the selected skeleton in the chosen base language.

Finally the system prompts the user to provide descriptions of the data structures and procedures required to turn the generic skeleton into a complete solution specification. Provided that these are consistent in terms of the selected language syntax, the "programming" task is now complete. To initiate a "run" of the program it only remains to indicate the location (in the local file system) of a data structure describing an instance of the problem, just as the name of a Pascal "file of records" might be specified conventionally.

At this point the system takes over. The data and compiled user code fragments are loaded across the parallel hardware together with the pre-defined system code required to implement the selected skeleton (this may already be present if the local memory is large enough). The hardware executes the skeleton, calling up user routines as appropriate, and returns an instance of the appropriate data structure (representing the results) to the file system. The mechanisms implementing this process are entirely hidden from the user.

A useful comparison can be made with the "routine library" facility, often found as part of a conventional programming model. Here, a collection of very specific (at least when compared with the skeletons) collection of program modules is provided. An appropriate selection of routines is made, and conventional language constructs are used to build these into a program which solves the problem. The user is required to conceive of and describe the overall solution, but is given help with the details. In contrast, the skeletal machine presents a collection of ready made (and invisibly implemented) frameworks. The programmer's task is to select one and fill in the details. Our long term goal is to attain the property of being "general-purpose" by providing a wide enough range of individually specialised options, rather than a single, all-purpose language.

### 2.3 Parallel Hardware

If our proposed system is to be shown to be genuinely useful, it will not be sufficient to show that each skeleton encapsulates a good parallel problem decomposition. It will also be necessary to show that an efficient distribution of this parallelism can be implemented on a realistic parallel machine. Subsequent chapters will sketch and analyse such implementations, which will all be described in terms of one machine model. This section introduces our choice of this underlying hardware. It must be emphasised that this selection and the corresponding implementation represents only one possible instantiation of our "skeletal machine". There is nothing inherent in the high level specifications which ties us to any particular model of parallel hardware. Many other possible implementations can be envisaged. Our purpose here is simply to show that one unarguably realistic implementation could be constructed.

As noted in section 1.1, the recent technological drive has been towards providing large scale replication of processing and storage elements, sharing the same design and fabrication processes. It is essential that the magnitude of these advances is not lost upon the designer of programming systems. Parallel implementations of abstract machines should be designed to make effective use of essentially indefinitely expandable numbers of significantly powerful components. Of course, any real machine sitting in the corner of a room is most definitely of a fixed, finite size. However, it is vital that systems be designed in such a way that substantial hardware expansion can be accommodated within a uniform framework. To design a highly efficient ten processor machine which grinds to a halt

when expanded to a hundred processors is to disregard the real significance of the new hardware. For this reason, performance analyses of the asymptotic (in the number of processors) type employed in this text must initially carry more weight than experimental or simulated results derived from small scale implementations. It is most important to get the broad principles right first and to worry about the details later.

The range of existing and proposed parallel hardware is diverse. However, to provide coverage of sufficient depth for the our purposes, it is possible to isolate the relationships between three types of hardware object as being of prime importance. These are the processing elements, the memory modules and the interconnection network.

The issue relating processing elements to memory modules concerns the question of whether particular elements are associated physically with particular modules. For example, the Computing Surface [25] is constructed from a collection of independent processor-memory pairs. Each processor has exclusive access to its own memory module at the hardware level – non-local access must be arranged by message passing in software. On the other hand, processors in the New York University Ultracomputer [12] are independent of any particular memory module. Access capability, via the network, is equally distributed. This equality is both a strength and a weakness. By removing the problems associated with arranging access to "distant" data it also prohibits any super-imposed system from exploiting locality to improve performance. In our selected hardware we take the former approach of associating each processor with a unique memory module. We will attempt to exploit this locality in our implementations.

The other important area concerns the network structure and its degree of integration with the processors and memories. In terms of structure, a wide variety of networks have been considered previously, ranging from the simplest "bus" scheme, in which every element competes for access to the single communication link, to complete interconnection schemes in which every element has a distinct connection to every other. Between these extremes range rings, grids, trees, shuffles hypercubes etc. In terms of integration we must decide whether processors and memory should be distributed throughout the network and active within it, or if they should they sit beside it, feeding in requests and receiving replies?

Again, the choice essentially concerns the presence or absence of a notion of locality. Once more, for our purposes, a decision is made in favour of its presence. Although we cannot hope to arrange for every memory access to refer exclusively to local memory, it should be possible to exploit some degree of near-neighbour

locality. This will only be possible if the notion of "neighbour" has any meaning and if the processors themselves influence the flow of data. Thus, in our selected hardware, processor-memory pairs will be located at the vertices of the selected network, actively forwarding non-local messages, requests and so on.

An immediate implication of this decision for the choice of a particular network is that the level of connectivity between physical elements must be sparse. Bearing in mind that we expect the number of processors and memories in use to be large, it is not reasonable to expect a single component (e.g. a bus) to connect directly to many other components and still provide reasonable performance. A wide variety of networks have been proposed as a basis for general purpose parallel computers, with consideration given to issues such as degree, diameter, optimal layout, wire length, regularity and fault-tolerance. The requirement for sparsity suggests that we should only consider networks whose degree grows as a small function of the number of elements, or even only those in which the degree is constant. Furthermore, the poor results for two dimensional layout, and consequently edge length, of most "logarithmic diameter" networks (e.g. as reported in [6]) make networks based on hypercubes, shuffles, etc. less attractive if we are looking towards direct hard-wired implementation as a long term goal. Of the regular networks with logarithmic diameter, only the tree appears to have a suitably concise layout (see chapter 3), but the potential bottleneck at the root and the long edges there count against it. Meanwhile, constant degree rings have a large diameter.

On the strength of these arguments the square grid, with its poorer than logarithmic diameter, but good degree, layout, wire length and regularity<sup>2</sup> is selected as a foundation for the parallel hardware to be used in the subsequent discussion on implementation. Since the relative importance of the factors considered is open to debate, it is not suggested that this choice is the only one possible. Instead, it is simply claimed that this model is unarguably realistic and practical. Other networks mentioned could equally well be used.

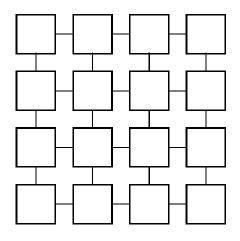

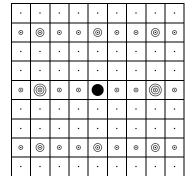

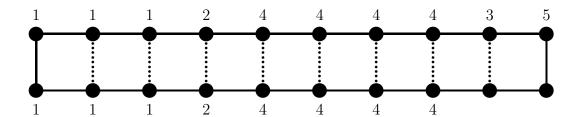

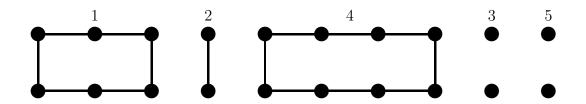

Figure 2.1 shows a small instance (with 16 processors) of the selected hard-ware<sup>3</sup>. Each square represents a standard sequential processor with its own memory. Lines connecting adjacent processors should be interpreted as bi-directional communication links, capable of transmitting a single word in each direction between the local memories of neighbours in unit time. In the style of the Inmos transputer [19], it is assumed that the processor instruction set includes "send"

<sup>&</sup>lt;sup>2</sup>And for that matter, fault tolerance, although this is not considered here.

<sup>&</sup>lt;sup>3</sup>For convenience, subsequent illustrations shrink the connecting links to have zero length, and represent the hardware as a simple grid.

Figure 2.1: A sixteen processor grid

and "receive" instructions which control the links, and that all four links may operate concurrently. None of the assumptions affect the asymptotic results obtained by more than a constant factor over those achievable with a more restricted model. Similarly, it can be assumed that all basic word instructions (from a typically "reasonable" instruction set) take unit time.

The communication links are assumed to follow the occam model [18]. Exchange of a datum only takes place when sending and receiving processors are ready to execute "send" and "receive" instructions respectively. The first processor ready is forced to wait for its neighbour. Thus, no notion of a global clock is provided or needed. Although we would expect identical devices to proceed at broadly the same rate, strict lock step operation is not required. Again, for the purposes of asymptotic analysis, any such minor discrepancies in clock speed can be glossed over since the synchronisation mechanism is sufficient to ensure correctness<sup>4</sup>.

In summary, the selected model of parallel hardware and the basic facilities which it provides may be seen to be entirely reasonable and realistic. There are no concealed tricks and the cost of any overheads is independent of the size of the machine considered, in terms of number of processors. For example, no unit time broadcast is assumed.

<sup>&</sup>lt;sup>4</sup>Although care must be taken to avoid deadlock, as in any parallel machine.

## 2.4 Implementation Structures and Performance Measures

#### 2.4.1 Building Skeleton Implementations

It has been emphasised in the preceding discussion that the skeletons comprising the overall framework are independent. Consequently, their implementations can be considered separately, as indeed they are for the four skeletons presented in chapters 3 to 6. This independence illustrates another useful property of this approach. By concentrating on the efficient implementation of several distinct and relatively simple systems, it is hoped to achieve better overall performance than can be obtained by implementing one monolithic system designed to handle all possibilities.

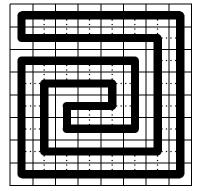

The implementation of each skeleton must ensure that the grid performs all the work described by the abstract specification. As well as the "real" computational tasks, this will involve dealing with the distribution of and access to non-local data, as implied by the distributed nature of the hardware. Fortunately, the problems associated with such a task are eased by the restricted nature of each individual skeleton – the pattern of work is clearer than for a more general system. Thus, each skeleton will have an associated controlling program, an appropriately parameterised copy of which is loaded (or given sufficient space, permanently sited) at each processor.

Execution of each skeleton can be decomposed into a sequence of phases. The controlling program, given knowledge of its processor's absolute location in the grid, determines this sequence of actions required of the processor to execute that particular skeleton. For example, at some point in a computation, data may be expected from one direction which must be manipulated and dispatched in another direction. The format of the data and the nature of the manipulation will vary from problem to problem, but its arrival and departure constitute structural properties of the skeleton, applicable in all instances.

Having loaded the controlling program, each processor must acquire a copy of the problem specific details and procedures as provided by the user. Since these are identical for each processor, it will be a simple task to arrange for copies of these to enter and sweep through the network. Similarly, the instance specific data is loaded to the local memories using the available external channels<sup>5</sup>.

<sup>&</sup>lt;sup>5</sup>The details of what lies beyond the grid are beyond our scope. The loading process described here is of no interest, being entirely dependent upon the external I/O systems provided, and is comparable with the process of booting a conventional machine and loading the memory. The crucial problems addressed here concern the control and manipulation of data required to

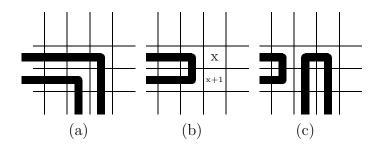

At this point, the system is ready to begin execution of the skeleton by having each processor execute the appropriate control program. Quite simply, this consists of a series of calls of the user specified procedures operating sequentially on local data, punctuated by a sequence of communications required to ensure the correct distribution and exchange of data between processors. As will become clear in subsequent chapters, such communications may take two forms, being either compulsory or optional.

In the former, the arrival, manipulation and dispatch of data form an inherent part of the skeleton's computational requirements. They can be guaranteed to occur in any problem instance using the skeleton. The synchronisation primitives described in section 2.3 are sufficient to be able to ensure that data transfer takes place only when both parties are ready and that it cannot be avoided.

In the latter example, a communication may or may not take place at some particular point in the computation, depending upon instance specific data. However, in any such case, it will be possible to reason that if no data arrives within a certain time period, that none will arrive during the phase. Such time periods are measured in terms of a number of local communication pulses. To ensure synchronisation, blank pulses will be filled by sending empty packets. In this way, pulses can be counted locally and suitable action taken. Note that this technique is only used when appropriate to a particular skeleton and not throughout the implementation of the whole machine, as might be required for a uniform general purpose abstraction.

Finally, the transformed data is dumped to the external system.

## 2.4.2 On Measuring Performance

#### 2.4.2.1 A Note on Notation

The  $0, \Omega, \Theta$  notation introduced by Knuth [21] is used throughout the text to indicate the asymptotic magnitude of various quantities. Thus, the statement

$$f\left(n\right) = O\left(g\left(n\right)\right)$$

means that there exist positive constants C and  $n_0$  with  $|f(n)| \leq Cg(n)$  for all  $n \geq n_0$ . Intuitively, and for our purposes more appropriately, this may be interpreted as meaning that f(n) "grows no faster than" g(n). Similarly,

$$f\left(n\right) = \Omega\left(g\left(n\right)\right)$$

produce solutions efficiently.

means that there exist positive constants C and  $n_0$  with  $|f(n)| \ge Cg(n)$  for all  $n \ge n_0$ , which may be interpreted as meaning that f(n) "grows at least as fast as" g(n). Finally,

$$f(n) = \Theta(g(n))$$

is true if and only if f(n) = O(g(n)) and  $f(n) = \Omega(g(n))$ , with the interpretation that the two functions "grow at the same rate".

#### 2.4.2.2 Performance Issues

In terms of performance, our interest is focussed on the efficiency with which a large grid of processors can implement each skeleton with respect to the performance of a single processor. Since the key issue is the introduction of large scale parallelism, it is important that more peripheral issues are not allowed to cloud the comparison. In particular, the machines at the nodes of the square grid should be identical to the uniprocessor machine against which their performance will be considered. This assumption has two implications which should be borne in mind when interpreting the performance analyses presented subsequently.

The first important point to note is the implicit assumption that the machine has "enough" memory to implement any instance of a given skeleton. Any complications introduced by a failure to meet this assumption would apply equally to sequential and parallel cases and would therefore serve only to hide the real issue of parallelism. Secondly, the assumption of "unit time" operations from the basic instruction set implies the unwritten corollary that asymptotic results obtained from the model apply only when the manipulated values can be represented within the word length of the machine. Once more, this applies equally to parallel and sequential implementations and to include extra terms to cater for this would again obscure the real issue. Thus, in a sequential machine it is assumed that the retrieval of an integer from memory is a unit time operation, rather than a  $\Theta(\log m)$  time operation where m is the magnitude of the integer. Similarly, it is assumed that the transfer of an integer between neighbouring processors is a unit time operation. Again, standard "fixes" to circumvent any real problems in practice would apply equally to sequential and parallel machines.

This second assumption requires one final note of caution which applies uniquely to parallel implementations. Some of the skeleton implementation algorithms to be presented make use of unique processor identifiers. At certain points these may be transferred between neighbours, using what is assumed to be a unit time operation. Strictly,  $\log_2 p$  bits are required to distinguish unique identifiers in a p processor machine and the unit time assumption is only valid when  $\log_2 p \leq w$ ,

the word length. For larger p, multiple transfers would be required increasing the time needed to  $\Theta(\log p)$  in such cases. However, a typical w of 32 or 64 allows  $p \leq 2^{32}$  or  $p \leq 2^{64}$  before this becomes an issue. Once again, the inclusion of such an addendum to relevant analyses would only complicate results in a way which would have little or no significance in practice – if a  $2^{32}$  processor 32 bit machine is considered feasible, then a small extension of the word length would not pose any serious difficulty.

## 2.5 Related Work

As was illustrated in chapter 1, the bulk of the work in the field addresses the problems of implementing universal languages, whether declarative or explicitly parallel. However, we can also identify a number of approaches which are more in the direction proposed here.

The most closely related work has focussed on the "divide and conquer" technique and its parallel implementation as a tree of processes. In particular, [22] characterizes a general form of "divide and conquer" as a higher order function and reports on a parallel implementation which dynamically maps the problem dependent process tree across a network of transputers. We will compare this work with that of our own skeletons in more detail in chapter 3.